本期分享Zynq-7010/20工业开发板(双核ARMCortex-A9+A7)的参数规格资料,其中包含软硬件、原理图、工业温度等均有。

测试板卡是一款基于XilinxZynq-7000系列XC7Z010/XC7Z020高性能低功耗处理器设计的异构多核SoC工业级核心板,处理器集成PS端双核ARMCortex-A9+PL端Artix-7架构28nm可编程逻辑资源。核心板内部集成USBPHY芯片,通过邮票孔连接方式引出千兆网口、USB、CAN、UART等通信接口,可通过PS端加载PL端程序,且PS端和PL端可独立开发。核心板经过专业的PCBLayout和高低温测试验证,稳定可靠,可满足各种工业应用环境。

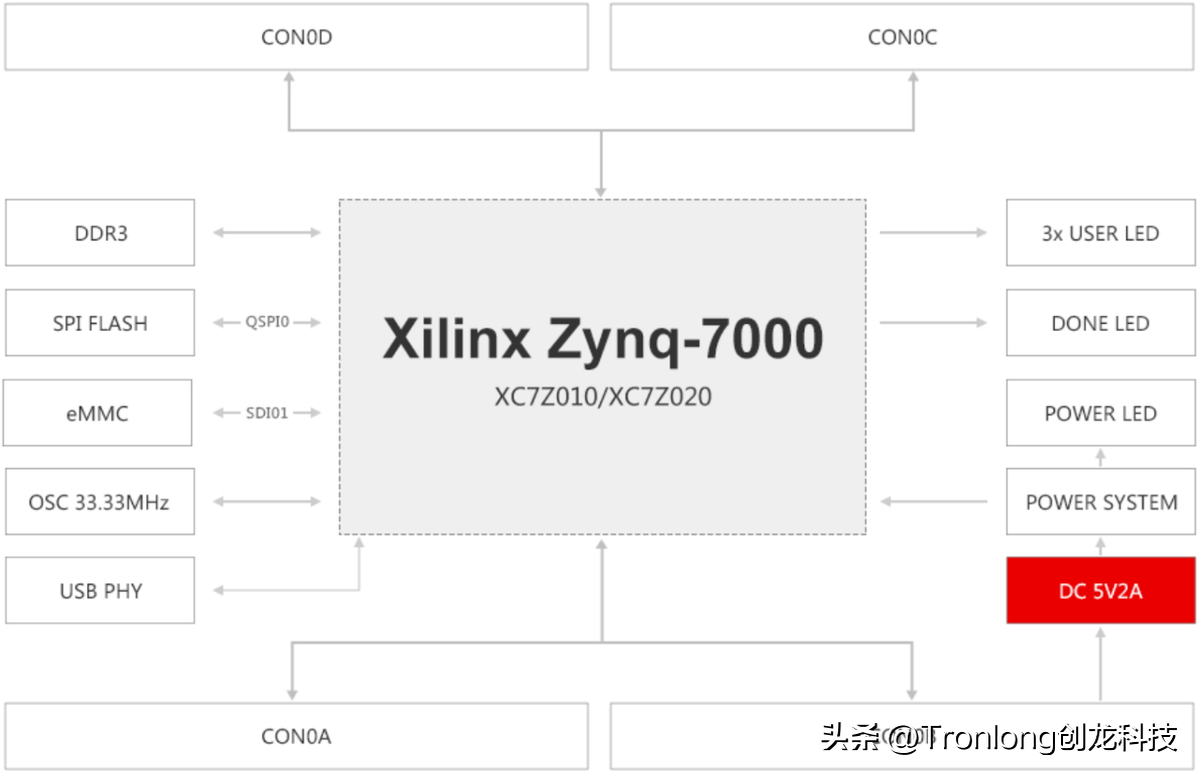

硬件资源SOM-TLZ7x-S核心板板载CPU、ROM、RAM、USBPHY、晶振、电源、LED等硬件资源,并通过邮票孔连接方式引出IO。

图1核心板硬件框图

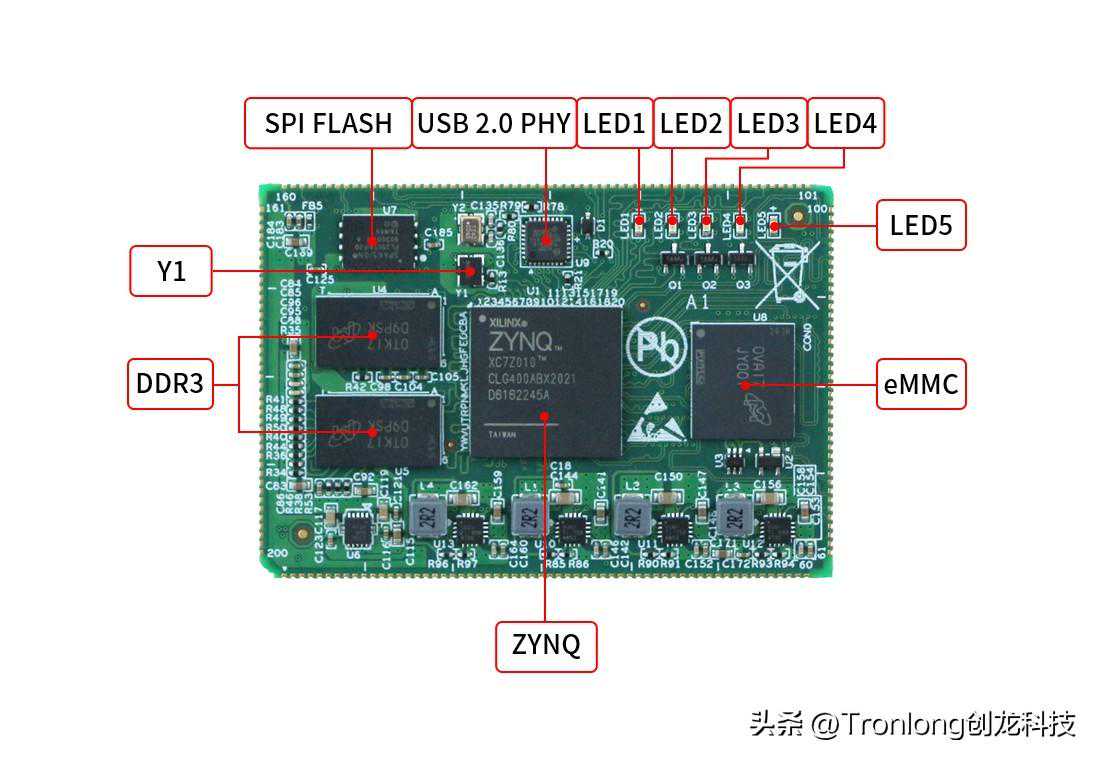

图2

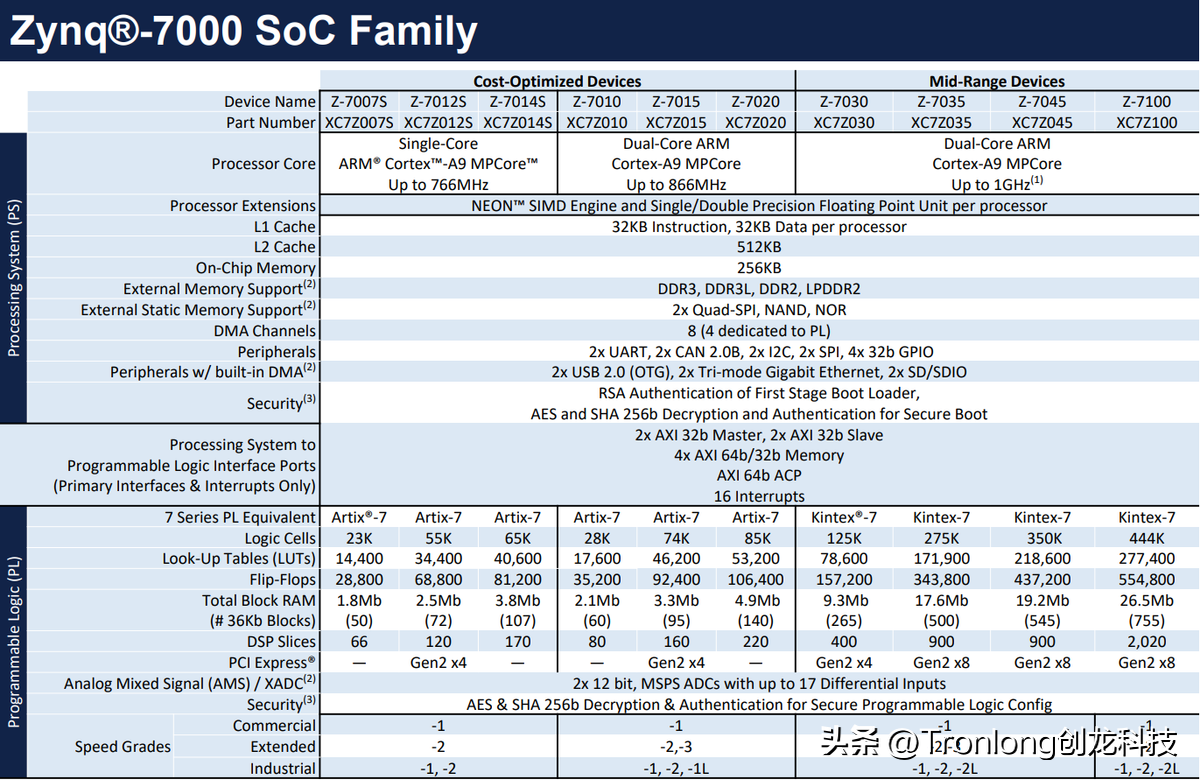

CPU核心板CPU型号兼容XC7Z010-2CLG400I/XC7Z020-2CLG400I,CLG400封装,工作温度范围为-40°C~100°C,引脚数量为400个,尺寸为17mm*17mm。

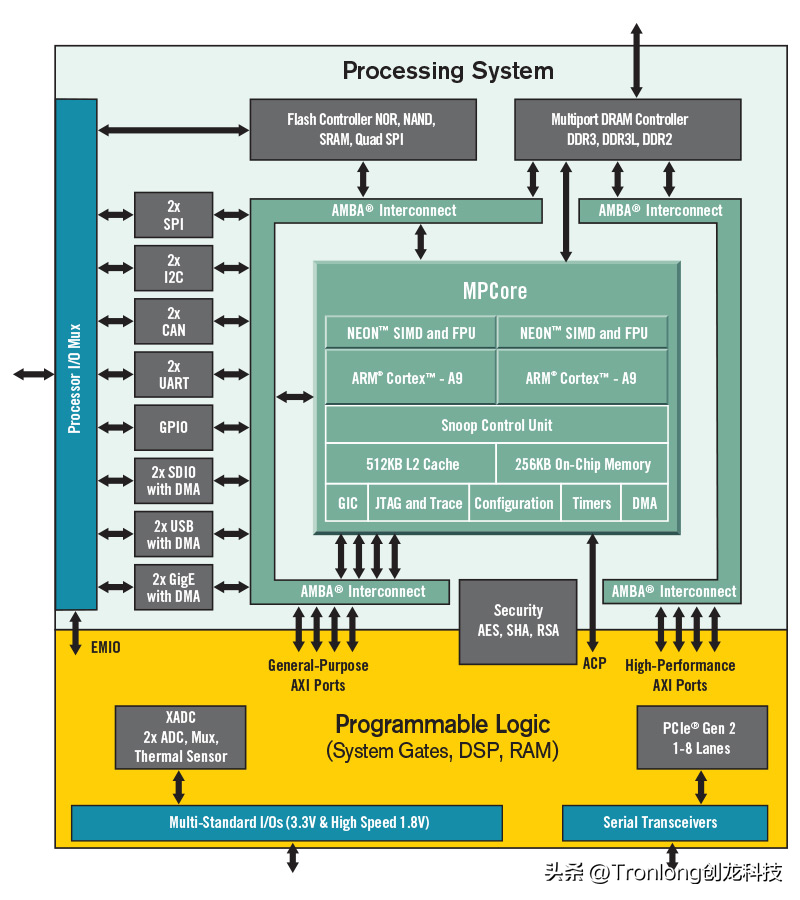

CPU功能框图、资源列表如下。

图3Zynq-7000处理器功能框图

图4Zynq-7000处理器资源列表

ROMSPINORFLASH核心板通过PS端的QSPI0(CS0)总线连接工业级SPINORFLASH,型号兼容CYPRESS公司的S25FL256S和旺宏电子(MXIC)的MX25L25645G,容量为256Mbit。

eMMC核心板通过PS端的SDIO1总线连接工业级eMMC,采用4bit数据线。

eMMC型号兼容Micron的MTFC4GACAJCN-4MIT(4GByte)和MTFC8GAKAJCN-4MIT(8GByte)、SkyHigh的S40FC004(4GByte)、SAMSUNG的KLM8G1GEUF-B04%(8GByte),以及江波龙(Longsys)的FEMDRW008G-88A39(8GByte)。

RAM核心板通过PS端的DDR总线连接2片工业级DDR3,每片采用16bit数据线,共32bit,容量支持512MByte/1GByte。

DDR3型号兼容Micron的MT41K128M16(256MByte)和MT41K256M16(512MByte),以及ISSI的IS43TR16128DL(256MByte)和IS43TR16256BL(512MByte),支持DDR3-1066工作模式(533MHz)。

晶振核心板采用2个工业级晶振Y1和Y2。

Y1为有源晶振,时钟频率为33.33MHz,频率稳定度为±20ppm,通过PS_CLK引脚为PS端提供系统时钟源。

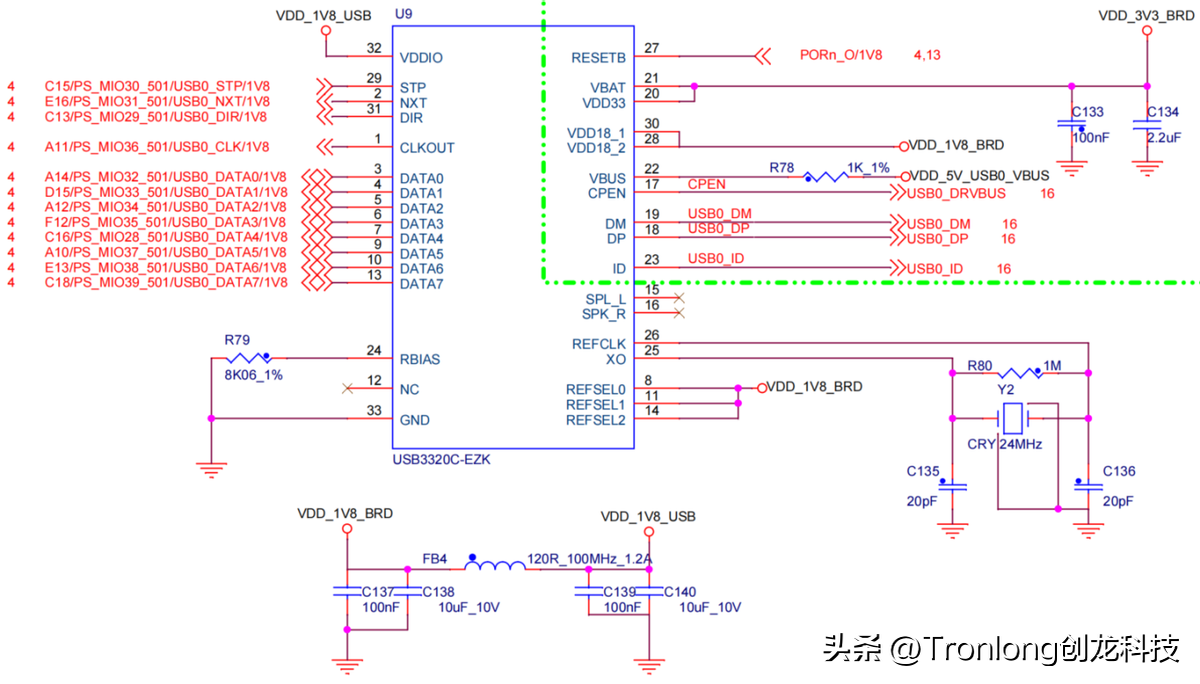

Y2晶振时钟频率为24MHz,频率稳定度为±30ppm,为PS端USBPHY提供时钟源。

电源核心板采用工业级分立电源芯片,满足系统的供电要求和CPU上电、掉电时序要求,采用5V直流电源供电。

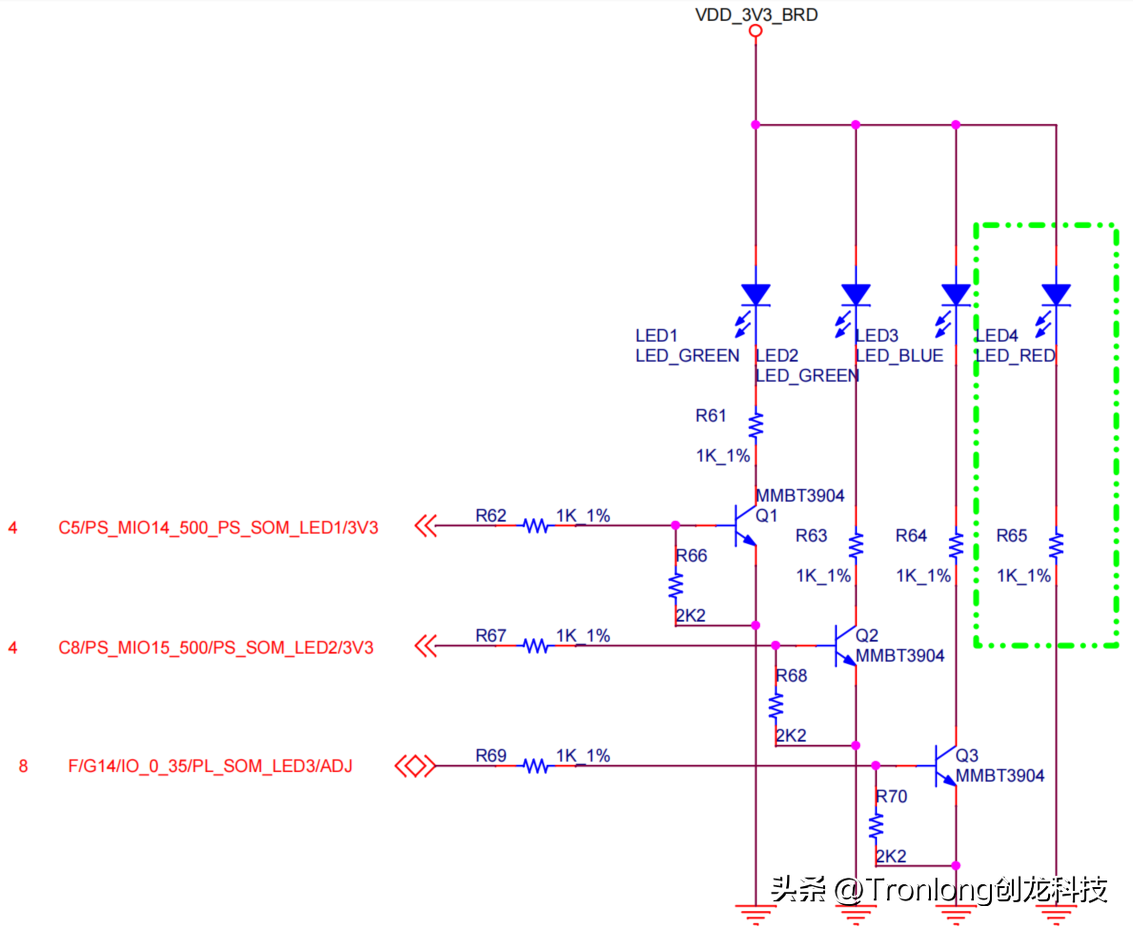

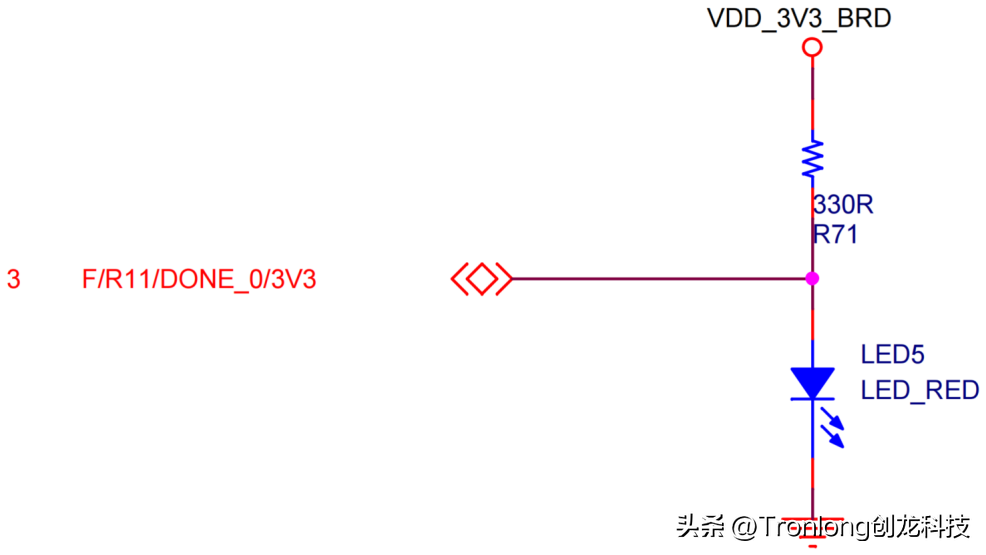

LED核心板板载5个LED。其中LED4为电源指示灯,系统上电完成后点亮;LED5为PL端DONE灯,当PL端初始化完成后会点亮;LED1和LED2为PS端用户可编程指示灯,LED3为PL端用户可编程指示灯,高电平点亮。

图5用户可编程指示灯与电源指示灯

图6PL端DONE灯

USBPHY核心板板载1个工业级,型号为USB3320C-EZK,支持USBHOST、Device和OTG功能。PS端的8位并行数据接口USB0ULPI通过PHY芯片转换成USB高速收发总线引出至邮票孔。

图7

外设资源核心板通过邮票孔引出的PS端主要外设资源、XADC资源如下表所示。大部分PS端外设均可通过EMIO方式使用PL端IO进行引出。

表1

外设资源

数量

性能参数

1

支持OTG模式;

支持High-Speed/Full-Speed/Low-Speed模式;

备注:核心板板载USBPHY已使用USB0;USB1相关引脚已被复用为SDIO0、SDIO1功能;

Ethernet

2

支持10/100/1000兆网口配置;

支持网络自适应;

SD/SDIO

1

支持//规范;

支持最高50MHz时钟;

备注:核心板板载eMMC设备已使用SDIO1;

SPI

2

支持MasterMode、SlaveMode、MultiMode;

每一路SPI支持3个片选;

最高支持50MHz工作频率;

UART

2

最高支持波特率为921600bps;

支持硬件或软件流控;

CAN

2

支持、标准;

最高支持1Mbit/s速率;

I2C

2

支持I2C总线规范2.0,支持100KHz、400KHz速率;

支持MasterMode、SlaveMonitorMode;

XADC

2

12位XADC,采样率高达1MSPS,unipolar模式支持0~1V输入,bipolar模式支持-0.5~0.5V输入;

一路支持获取芯片结温和CPU若干供电电压;

一路提供17对差分输入,包含1对专用模拟差分输入,16对复用模拟差分输入;

引脚说明核心板CPU型号兼容XC7Z010和XC7Z020,其中XC7Z010引出PL端3个单端IO,48对差分对IO,共99个IO;XC7Z020引出PL端4个单端IO,60对差分对IO,共124个IO。XC7Z010和XC7Z020的PS端均引出31个PS端的单端IO。

备注:部分芯片引脚号后面括号标注NC的(详情见引脚列表),表示CPU为XC7Z010的核心板未引出该信号,而CPU为XC7Z020的核心板则不受影响(即引出该信号)。

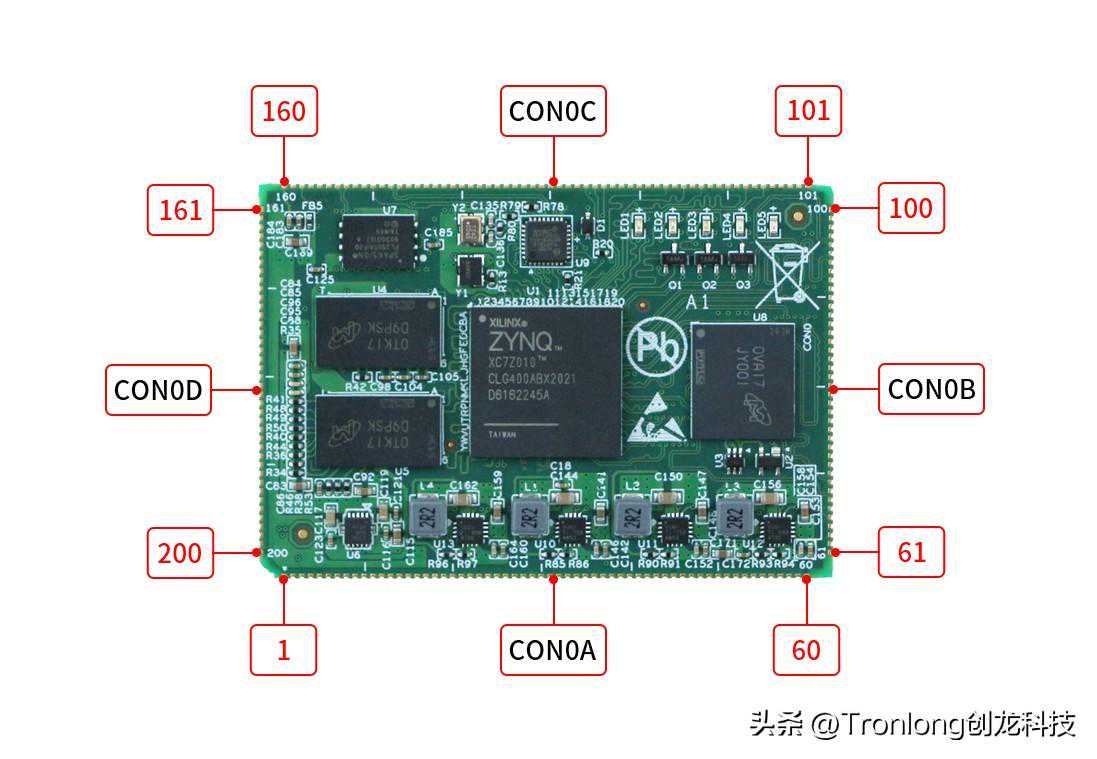

引脚排列核心板邮票孔引脚采用2x40pin+2x60pin分布,共200pin。核心板左下角为第1pin,以逆时针方向递增至200pin,各个边依次为CON0A、CON0B、CON0C、CON0D。

图8核心板引脚排列示意图

电气特性工作环境表2

环境参数

最小值

典型值

最大值

工作温度

-40°C

/

85°C

存储温度

-50°C

/

90°C

工作湿度

35%(无凝露)

/

75%(无凝露)

存储湿度

35%(无凝露)

/

75%(无凝露)

工作电压

/

5.0V

/

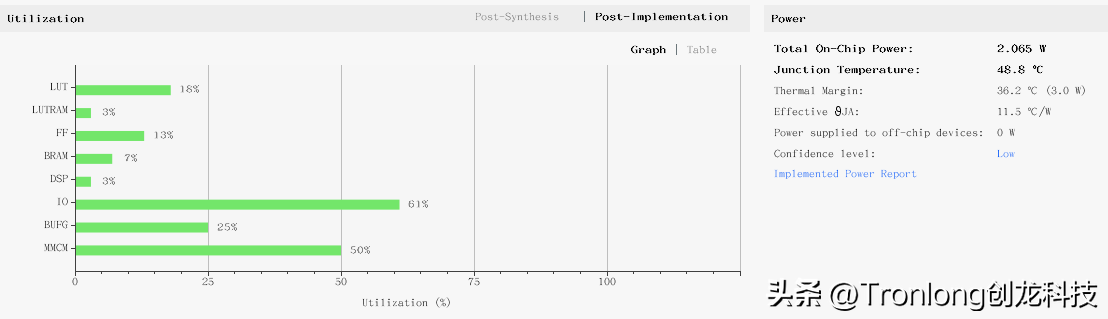

功耗测试表3

类别

电压典型值

电流典型值

功耗典型值

状态1

5.0V

0.27A

1.35W

状态2

5.0V

0.49A

2.45W

备注:功耗基于TLZ7x-EasyEVM-S评估板测得。功耗测试数据与具体应用场景有关,测试数据仅供参考。

状态1:评估板不接入外接模块,PS端启动系统,不执行额外应用程序;PL端运行LED测试程序。

状态2:评估板不接入外接模块,PS端启动系统,运行DDR压力读写测试程序,2个ARMCortex-A9核心的资源使用率约为100%;PL端运行IFD综合测试程序。

图9状态2PL端资源使用率

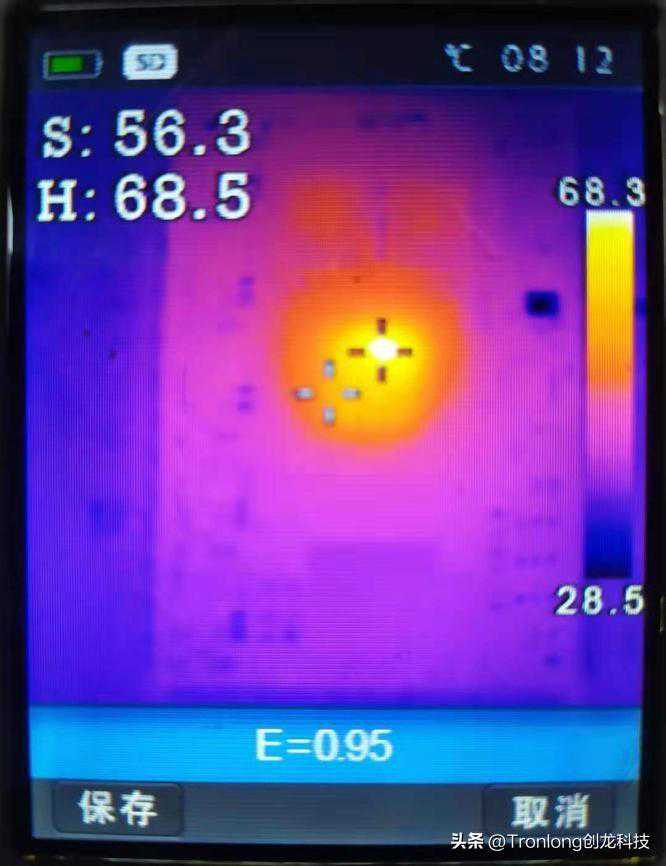

热成像图核心板未安装散热片与风扇,在常温环境、自然散热、“状态2”下稳定工作10min后,测试核心板热成像图如下所示。H为最高温度,S为平均温度。

备注:不同测试条件下结果会有所差异,数据仅供参考。

图10

请参考以上测试结果,并根据实际情况合理选择散热方式。

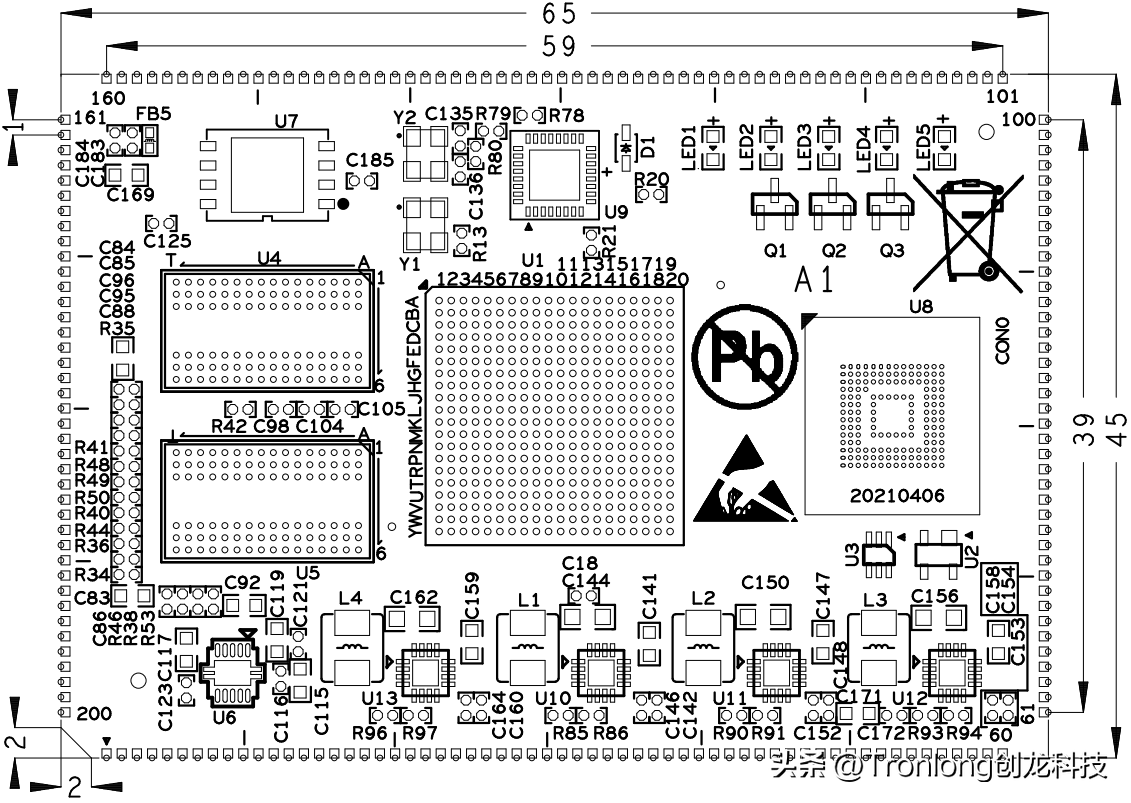

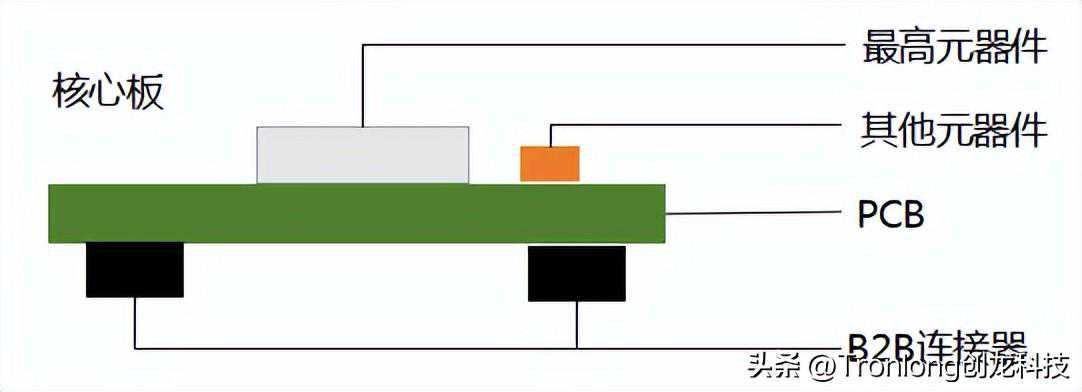

机械尺寸表4

PCB尺寸

45mm*65mm

PCB层数

10层

元器件最高高度

3.0mm

PCB板厚

1.2mm

图11

图12

元器件最高高度:指核心板最高元器件水平面与PCB正面水平面的高度差。核心板最高元器件为功率电感(L1/L2/L3/L4)。

底板设计注意事项最小系统设计基于SOM-TLZ7x-S核心板进行底板设计时,请务必满足最小系统设计要求,具体如下。

电源设计说明核心板电源设计说明

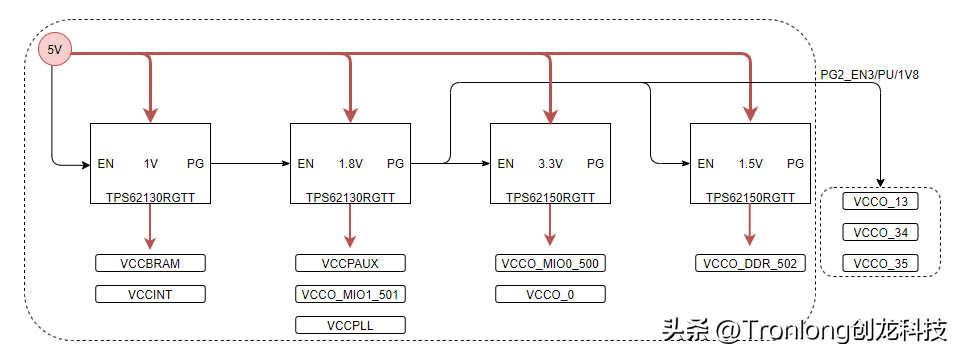

核心板电源电路为VCCBRAM、VCCINT提供1V供电;为VCCPAUX、VCCO_MIO1_501、VCCPLL提供1.8V供电;为VCCO_MIO0_500、VCCO_0提供3.3V供电;为VCCO_DDR_502提供1.5V供电。

图13

核心板采用工业级电源芯片将5V分别转成1V、1.8V、3.3V、1.5V,且通过电源芯片的EN和PG引脚进行控制上电时序,顺序依次为:1其他BANK电源。系统上电时,通过3.3V电源的PG信号控制PS_POR_B_500,以满足PS_POR_B_500在各路PS供电电源上电过程中处于低电平状态的要求。

备注:系统掉电时,通过电压监测芯片实现PS_POR_500在VCCINT掉电过程中处于低电平状态。

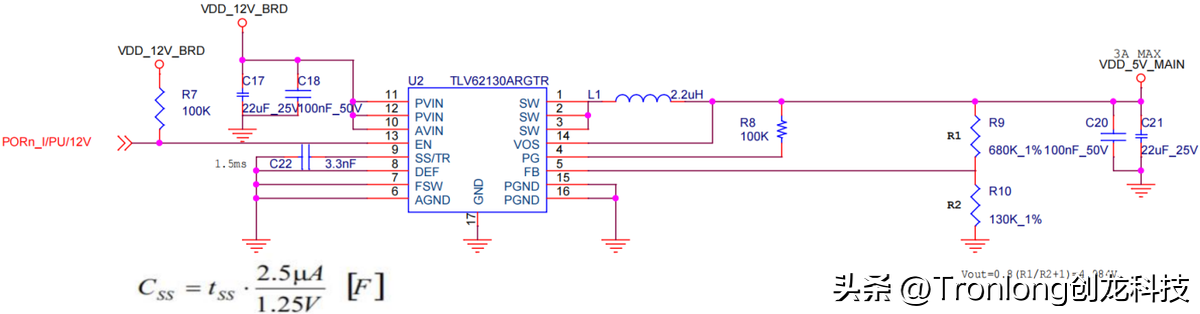

核心板主输入电源

VDD_5V_MAIN为核心板的主供电输入,输入电源功率建议按最大10W设计。

备注:由于VDD_5V_MAIN需满足评估底板其他5V外设接口的供电需求,因此评估板采用15W进行设计。

图14

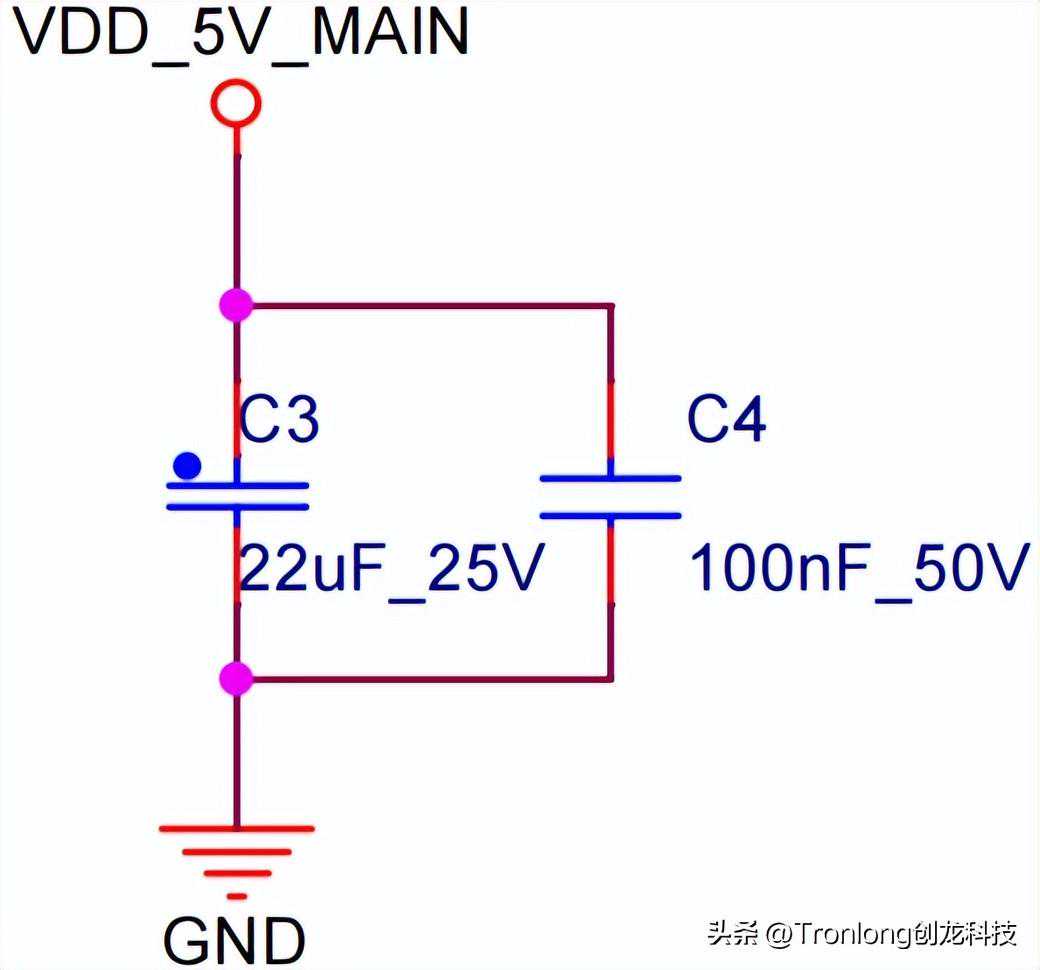

为保证VDD_5V_MAIN的电源稳定,底板设计时请参照评估板原理图,在靠近邮票孔VDD_5V_MAIN电源输入引脚位置放置储能、滤波电容。

图15

XADC电源

XADC在核心板内部已设计1.8V供电,使用CPU内部参考电源。

VCCBATT电源

VCCBATT电源在核心板内部已设计1.8V供电,设计时无需提供额外供电给该引脚,默认悬空处理即可。

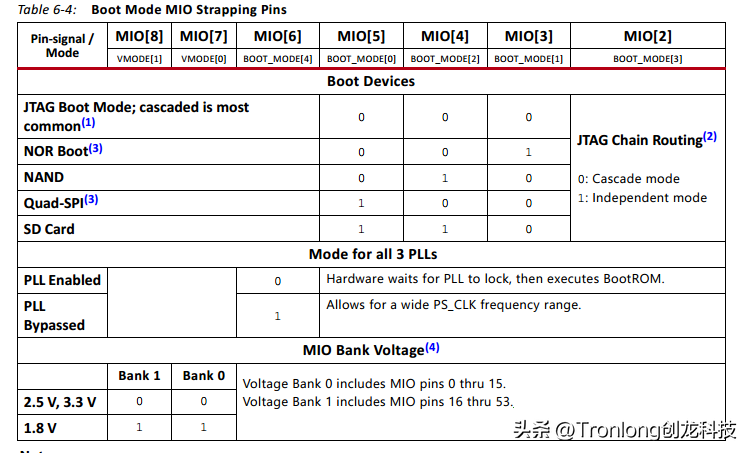

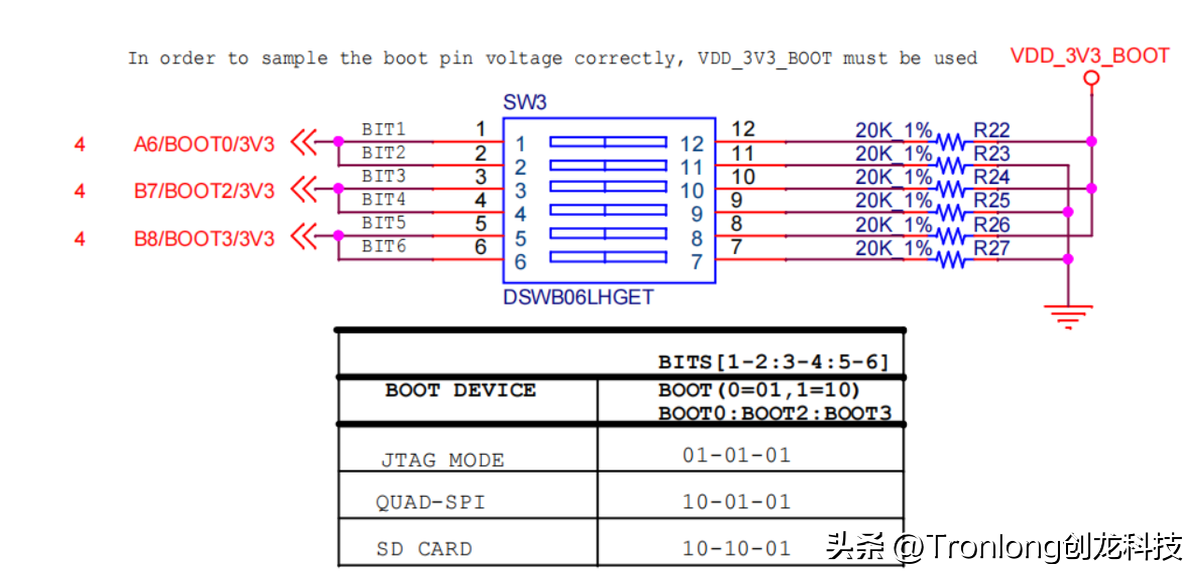

系统启动配置核心板PS端BOOTSET引脚为MIO[8:2],说明如下图所示。其中BOOTSET引脚与QSPI0总线存在复用关系,MIO[8:7]配置与BANK0、BANK1电源电压有关,请保证BOOTSET引脚在上电初始化过程中不受外接设备的影响,否则将会导致PS端无法正常启动及核心板功能异常。

图16

BOOTSET引脚(MIO3、MIO6、MIO7、MIO8)在核心板内部已进行上下拉配置,详细配置说明请查看“引脚上下拉说明”小节。底板BOOTSET引脚上拉电源需使用VDD_3V3_BOOT以保证正确读取BOOTSET引脚的电平状态。设计系统启动配置电路时,请参考评估底板BOOTSET部分电路进行相关设计。

图17

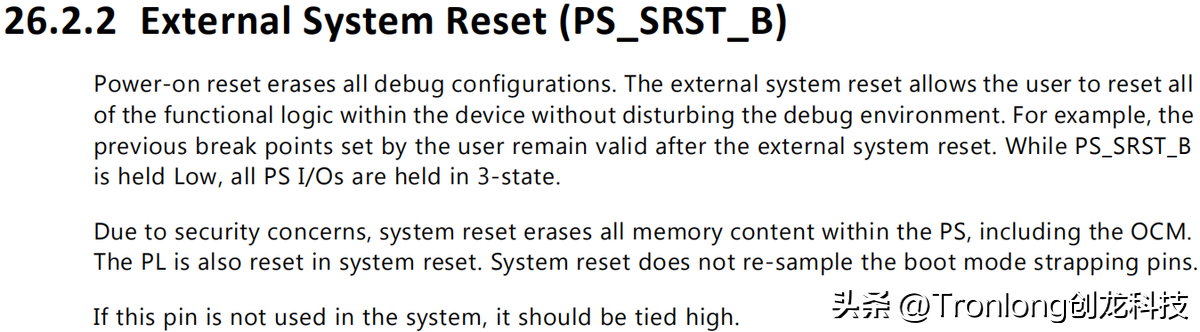

系统复位信号PS_SRST_B_501

PS_SRST_B_501为系统复位输入引脚,使用该信号对系统进行复位时,会复位除调试环境外的所有功能逻辑,PL端逻辑也会被复位。

PS_SRST_B_501信号在核心板已上拉,详细配置说明请查看“引脚上下拉说明”小节,在系统启动过程中拉低该引脚会导致系统无法启动,默认情况悬空处理即可。

图18

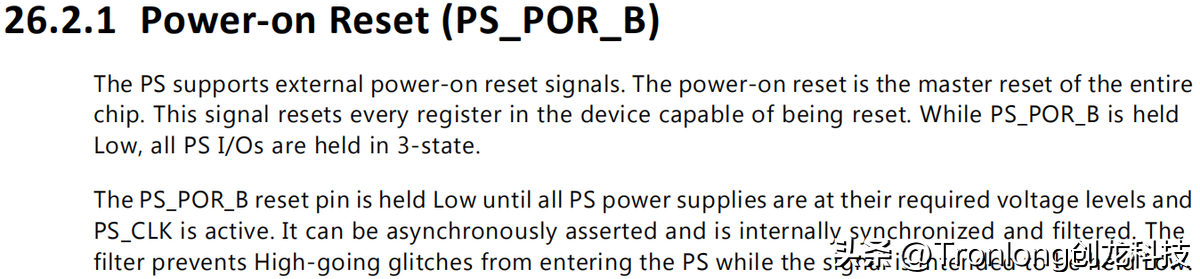

PS_POR_B_500

PS_POR_B_500为PS端PowerOnReset输入引脚,该复位信号不但复位所有寄存器,还将复位所有调试环境。

图19

核心板内部已对PS_POR_B_500设计上下电控制电路,底板无需针对该引脚进行相关设计。

PORn_O

PORn_O信号为核心板电源复位输出,将会在核心板上电过程中一直保持低电平,可使用该信号作为评估底板各部分功能的复位引脚。

PROGRAM_B

PROGRAM_B信号用于复位PL端逻辑。核心板内部已上拉4.7K电阻至3.3V电源,默认情况悬空处理。

其他配置信号BANK34中的PUDC_B为PL端IO启动上拉使能配置引脚,在核心板内已上拉,详细配置说明请查看“引脚上下拉说明”小节。

图20

其他设计注意事项保留MicroSD卡接口评估底板通过SDIO0总线引出MicroSD卡接口,主要用于调试过程中使用Linux系统启动卡来启动系统,或批量生产时可基于MicroSD卡快速固化系统,底板设计时建议保留此外设接口。

保留UART接口评估底板将PS端和PL端的调试串口引脚通过CP2105芯片引出至MicroUSB接口。PS端调试串口为UART1,PL端调试串口TX与RX引脚分别为F/D19/IO_L4P_T0_35/ADJ、F/D20/IO_L4N_T0_35/ADJ。底板设计时建议PS端保留UART1作为系统调试串口。

保留JTAG接口评估底板引出14pinJTAG接口,为便于系统的调试,底板设计时建议保留此接口,且JTAG接口信号走线长度要求尽可能短。

XADC电路设计核心板引出了XADC采样通道:DXP/N、VP/VN、AD0P/N~AD15P/N。设计需注意:

XADC使用内部参考电压,VREFP_0和VRFN_0已连接至GND。VCCADC_0已设置为1.8V供电。

XADC接口支持两种模式输入,unipolar模式支持幅值为0~1V信号输入,bipolar模式支持幅值为-0.5~0.5V输入,输入信号请勿超过以上范围,否则可能会损坏核心板。

如无需使用DXP/N、VP/VN通道,请将DXP_0_TMP、DXN_0_TMP、VP_0_ADC/VN_0_ADC引脚接地。

免责声明:本文章如果文章侵权,请联系我们处理,本站仅提供信息存储空间服务如因作品内容、版权和其他问题请于本站联系